El mayor fabricante chino de chips está a punto de iniciar la producción en 5 nm. Su plan es tener los 3 nm en 2026

- 1 Días, 8 Horas, 26 Minutos

- Xataka.com

- Tecnología

El mayor fabricante chino de chips está a punto de iniciar la producción en 5 nm. Su plan es tener los 3 nm en 2026

A SMIC (Semiconductor Manufacturing International Corp), el mayor fabricante chino de semiconductores, le ha costado más de dos años refinar su tecnología de integración más avanzada lo necesario para producir circuitos integrados de 5 nm. Y no ha recorrido solo este camino. Lo ha transitado de la mano de Huawei. La doctora Kim, una experta en la fabricación de chips que ha trabajado en Samsung y que actualmente investiga para TSMC en EEUU, sostiene que SMIC está a punto de iniciar la producción de chips de 5 nm.

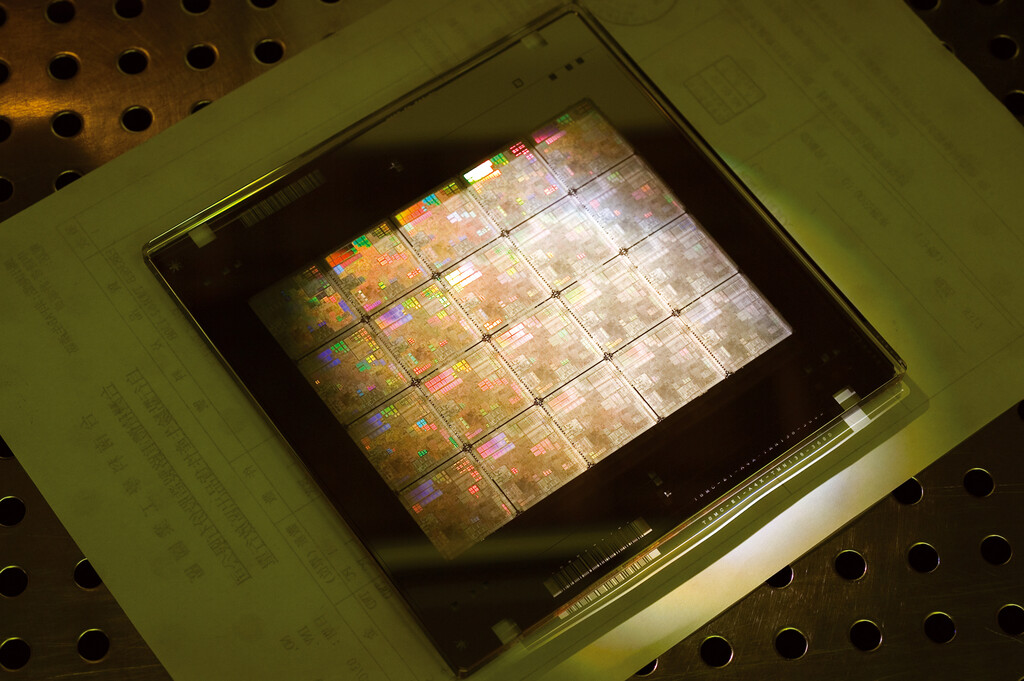

Es perfectamente creíble porque, como acabamos de ver, sabemos con certeza que esta compañía lleva varios años trabajando en esta tecnología. Y, además, la doctora Kim es una fuente fiable. Sin embargo, esta experta ha apuntado algo crucial que no debemos pasar por alto: el rendimiento por oblea que ha alcanzado actualmente SMIC en sus nodos de 5 nm es inferior al 30%. Cuando los fabricantes de semiconductores producen una oblea de chips algunos de esos núcleos no funcionan correctamente. Es lo normal.

Y cuando ponen en marcha un nuevo nodo litográfico su rendimiento por oblea suele tener un margen de mejora amplio, pero poco a poco, a medida que los ingenieros van refinando sus procesos de integración, este parámetro mejora. Una litografía madura puede entregar a los fabricantes de circuitos integrados un rendimiento muy alto, pero una tecnología incipiente suele moverse en la órbita del 50% de rendimiento, por lo que solo la mitad de los chips producidos funciona correctamente.

Los chips de 3 y 5 nm de SMIC son posibles gracias a la técnica SAQP

El problema es que para que una tecnología de integración sea rentable desde un punto de vista económico su rendimiento por oblea tiene que ser de al menos el 70%. Y, como acabamos de ver, la doctora Kim sostiene que el nodo de 5 nm de SMIC está por debajo del 30%. Objetivamente es un rendimiento muy pobre, pero sabemos qué explica esta cifra tan baja: la técnica empleada por este fabricante para producir estos semiconductores. Se conoce como multiple patterning, y SMIC la utiliza desde hace más de un año y medio para fabricar chips de 7 nm para Huawei y otros clientes.

Los chips de 5 nm que SMIC va a fabricar para Huawei son posibles gracias a una tecnología conocida como SAQP

Esta estrategia consiste en transferir el patrón a la oblea en varias pasadas con el propósito de incrementar la resolución del proceso litográfico. Funciona, pero es la responsable de que el rendimiento por oblea sea claramente mejorable. No obstante, con toda probabilidad los circuitos integrados de 5 nm que presumiblemente SMIC va a fabricar próximamente para Huawei son posibles gracias a una tecnología conocida como SAQP (Self-Aligned Quadruple Patterning), que no es más que un multiple patterning más agresivo y sofisticado que el utilizado para fabricar el SoC Kirin 9000S de 7 nm y otros chips.

Un informe publicado hace dos días por el medio taiwanés Economic Daily News asegura que SMIC va a iniciar la fabricación de semiconductores de 3 nm equipados con transistores de tipo GAA (Gate-All-Around) para Huawei en 2026. No obstante, esto no es todo. Este artículo también sostiene que esta última compañía ya ha completado las pruebas de laboratorio que persiguen hacer posible la fabricación de circuitos integrados utilizando nanotubos de carbono. El plan de Huawei presumiblemente es ceder esta innovación a SMIC para adaptarla a la producción a gran escala.

El enorme esfuerzo que están haciendo Huawei, SMIC y otras compañías chinas involucradas en el diseño y la fabricación de semiconductores es el resultado de su incapacidad de acceder a los equipos de fotolitografía de ultravioleta extremo (UVE) que produce la compañía neerlandesa ASML a causa de las sanciones de EEUU. Con estas máquinas SMIC podría fabricar chips de 3 y 5 nm entregando un rendimiento por oblea similar al que han alcanzado TSMC o Samsung.

Sin embargo, la necesidad de producir estos circuitos integrados utilizando los equipos de ultravioleta profundo (UVP) de ASML, que son menos sofisticados, les obliga a recurrir a la técnica SAQP. Funciona, como hemos visto, pero estas compañías pierden mucha competitividad debido al pobre rendimiento por oblea y el elevado coste que conlleva esta tecnología.

Más información | Economic Daily News

-

La noticia

El mayor fabricante chino de chips está a punto de iniciar la producción en 5 nm. Su plan es tener los 3 nm en 2026

fue publicada originalmente en

Xataka

por

Juan Carlos López

.

0 Comentarios